## الجمهورية الجزائرية الديمقراطية الشعبية

#### REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

وزارة التعليم العالى والبحث العلمي

MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

UNIVERSITE DE TLEMCEN

FACULTE DE TECHNOLOGIE

DEPARTEMENT DE GENIE ELECTRIQUE ET ELECTRONIQUE

جامعة أبي بكر بلقايد – تلمسان – كلية التكنولوجيا

قسم الهندسة الكهربائية والإلكترونية

# ARCHITECTURE DES ORDINATEURS

Note de Cours et Exercices

Dr. BETAOUAF Talib Hicham

2EME ANNEE LICENCE EN PRODUCTIQUE FILIÈRE GÉNIE INDUSTRIEL Université de Tlemcen Année Universitaire 2020/2021

## Architecture des Ordinateurs

# Note de Cours et Exercices 2<sup>ème</sup> Année Licence en Productique Filière Génie Industriel

Dr. BETAOUAF Talib Hicham

#### **Avant-propos**

Ce document est inspiré d'un enseignement délivré depuis plusieurs années aux étudiants en 2<sup>ème</sup> année de Licence en Productique. Il regroupe toutes les notions essentielles à l'architecture des ordinateurs sous forme de collections de notes et de mots clés faciles à retenir pour l'étudiant. Ces notes de cours résument très sommairement les points importants abordés en cours.

L'objectif est de faire comprendre les mécanismes internes de l'ordinateur et leurs implications sur l'environnement informatique aux étudiants de licence, et de façon plus générale de faire découvrir l'architecture des machines à tous ceux qui s'intéressent à ce sujet.

Ce recueil a pour ambition d'aider l'étudiant à mieux assimiler les notions vues en cours et en TD grâce aux photographies et schémas illustratifs. Il est organisé en quatre chapitres qui couvrent la totalité du programme de la matière.

A la fin de chaque chapitre du polycopié, des séries d'exercices sont proposées pour des travaux dirigés. Ces exercices peuvent aussi servir comme soutient aux étudiants pour la révision lors des contrôles d'évaluation.

L'auteur remercie chaleureusement ses collègues, Dr MENADJLIA Nardjes, maître de conférences à l'université de Tlemcen et Mr BELKHERROUBI Mustafa Kamel maître assistant à l'université de Tlemcen, d'avoir expertisé ce travail et leur exprime son immense gratitude pour toutes leurs remarques et suggestions pertinentes dans le but d'améliorer la qualité de ce document.

# Table des matières

| AVA         | NT-P   | ROPOS                                                        | 2  |

|-------------|--------|--------------------------------------------------------------|----|

| INT         | RODU   | JCTION                                                       | 5  |

| CHA         | APITF  | RE 1 : GENERALITES SUR L'ORDINATEUR                          | 6  |

| 1. H        | Iistoi | RE DES ORDINATEURS                                           | 6  |

|             | A.     | LA GENERATION ZERO: LES CALCULATEURS MECANIQUES (AVANT 1945) | 6  |

|             | В.     | LA PREMIERE GENERATION: LES TUBES A VIDE (1945 - 1955)       |    |

|             | C.     | La deuxieme generation : les transistors (1955 - 1965)       | 8  |

|             | D.     | LA TROISIEME GENERATION: LES CIRCUITS INTEGRES (1965 - 1973) |    |

|             | Ε.     | LA QUATRIEME GENERATION: LES MICROPROCESSEURS (1971 - 1980)  | 8  |

|             | F.     | AUJOURD'HUI: LA LOI DE MOORE EST ENCORE D'ACTUALITE          | 9  |

| 2. S        | TRUC   | TURE DE BASE D'UN ORDINATEUR                                 | 9  |

|             | A.     | DEFINITIONS                                                  | 9  |

|             | В.     | ARCHITECTURE DE JOHN VON NEUMANN                             | 10 |

|             | C.     | ARCHITECTURE EN COUCHES                                      | 10 |

|             | D.     | L'ORDINATEUR DU POINT DE VUE INTERNE                         | 11 |

| 3. R        | EPRE   | SENTATION ET CODAGE DE L'INFORMATION                         | 18 |

|             | A.     | CODAGE DE L'INFORMATION                                      | 18 |

|             | В.     | SYSTEME DE NUMERATION                                        | 18 |

|             | C.     | CODAGE DES NOMBRES                                           | 21 |

|             | D.     | CODAGE DES CARACTERES                                        | 26 |

|             | E.     | CODAGE D'UNE IMAGE                                           | 27 |

|             | F.     | CODAGE DU SON                                                | 28 |

| EXE         | ERCIO  | CES                                                          | 29 |

| CHA         | APITF  | RE 2 : LOGIQUE COMBINATOIRE ET SEQUENTIELLE                  | 30 |

| 1. C        | CIRCUI | TS LOGIQUES                                                  | 30 |

|             | A.     | FONCTIONS LOGIQUES ELEMENTAIRES                              |    |

|             | В.     | REGLES DE CALCUL                                             | 32 |

|             | C.     | CONSTRUCTION ET OPTIMISATION                                 | 32 |

| <b>2.</b> C | CIRCUI | TS COMBINATOIRES                                             | 36 |

|             | A.     | DEFINITIONS                                                  | 36 |

|             | В.     | CARACTERISTIQUES                                             | 36 |

|             | C.     | CIRCUITS COMBINATOIRES DE BASE                               | 37 |

| <b>3.</b> C | CIRCUI | TS ARITHMETIQUES                                             | 40 |

|             | A.     | Demi-additionneur                                            | 40 |

|             | В.     | ADDITIONNEUR COMPLET                                         | 41 |

|             | C.     | Unite Arithmetique et Logique                                | 41 |

| <b>4.</b> C | CIRCUI | TS SEQUENTIELS                                               | 43 |

|             | ٨      | DEFINITIONS                                                  | 43 |

|      | В.      | LES BASCULES                              | 44         |

|------|---------|-------------------------------------------|------------|

|      | C.      | LES REGISTRES                             | 49         |

| 10.1 | VEDCIC  | NEC.                                      | <b>~</b> 0 |

| Εž   | XERCIC  | TES                                       | 50         |

| Cl   | HAPITR  | EE 3 : MEMOIRES                           | 52         |

| 1.   | DEFINI  | ΓΙΟΝS                                     | 52         |

| 2.   | CARAC   | TERISTIQUES                               | 52         |

|      | A.      | CAPACITE D'UNE MEMOIRE                    | 52         |

|      | В.      | VOLATILITE                                | 53         |

|      | С.      | MODE D'ACCES A L'INFORMATION              | 53         |

|      | D.      | TEMPS D'ACCES                             | 53         |

| 3.   | TYPES   | DE MEMOIRES                               | 54         |

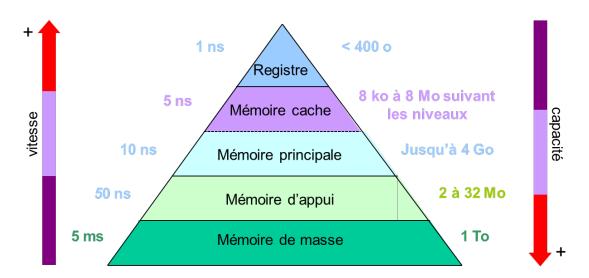

|      | A.      | LES REGISTRES                             | 54         |

|      | В.      | LA MEMOIRE CACHE                          | 54         |

|      | C.      | LA MEMOIRE PRINCIPALE                     | 54         |

|      | D.      | LA MEMOIRE D'APPUI                        | 54         |

|      | Ε.      | LA MEMOIRE DE MASSE                       | 54         |

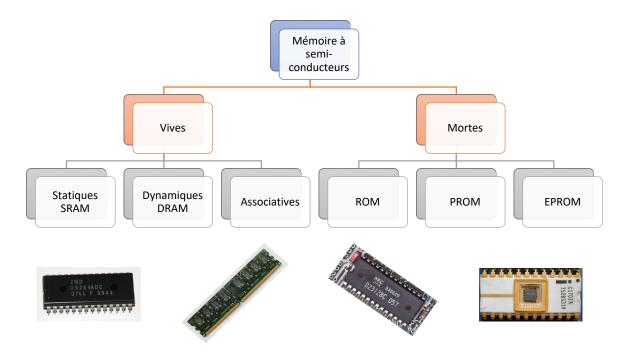

|      |         | FICATION DES MEMOIRES                     |            |

| 5.   |         | RE CENTRALE                               |            |

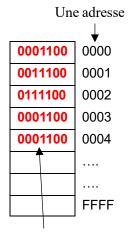

|      | A.      | VUE LOGIQUE DE LA MEMOIRE CENTRALE        |            |

|      | В.      | STRUCTURE PHYSIQUE D'UNE MEMOIRE CENTRALE | 56         |

| E    | XERCIC  | ES                                        | 58         |

| Cl   | HAPITR  | RE 4 : PROCESSEURS                        | 59         |

| 1.   | Micro   | PROCESSEUR                                | 59         |

|      |         | TECTURE INTERNE                           |            |

|      | A.      | L'UNITE DE COMMANDE                       | 60         |

|      | В.      | L'UNITE DE TRAITEMENT                     | 61         |

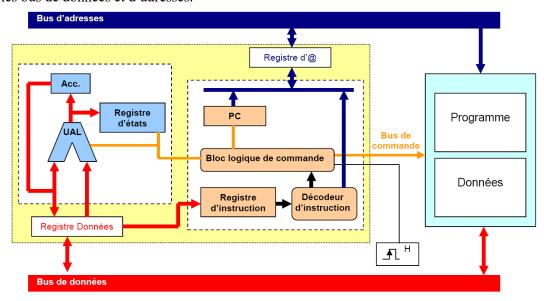

|      | C.      | LES BUS DE COMMUNICATION                  | 61         |

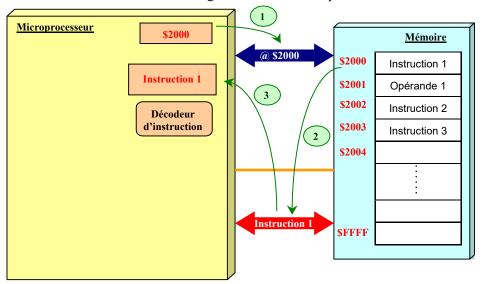

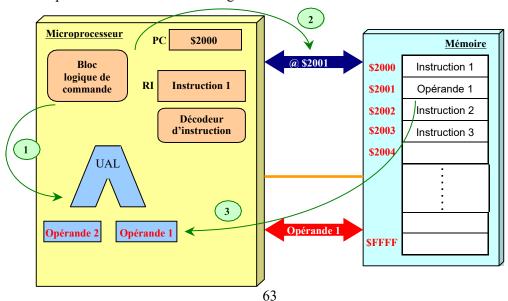

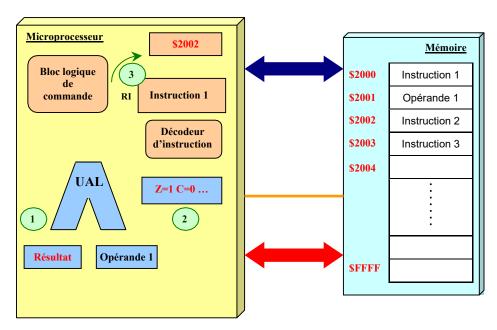

| 3.   | CYCLE   | D'UNE INSTRUCTION                         | 63         |

| 4.   | JEU D'I | NSTRUCTIONS                               | 64         |

|      | A.      | DEFINITION                                | 64         |

|      | В.      | TYPE D'INSTRUCTIONS                       | 64         |

|      | С.      | CODAGE                                    | 65         |

|      | D.      | MODE D'ADRESSAGE                          | 65         |

|      | Е.      | NOTION D'ARCHITECTURE RISC ET CISC        | 66         |

| E    | XERCIC  | TES                                       | 68         |

| RΙ   | EFEREN  | ICES                                      | 69         |

#### Introduction

L'informatique, qui est l'une des principales disciplines intégrées à la productique, est une science centrée sur l'ordinateur. Tout spécialiste en productique doit maîtriser le fonctionnement de bas niveau d'un ordinateur pour la mise en œuvre et le perfectionnement des systèmes de production automatisés.

L'architecture des ordinateurs est une science qui permet d'étudier les différents composants internes des machines, expliquant leur construction et leurs interactions. Un ordinateur est un instrument complexe capable d'effectuer diverses tâches et dont les performances globales dépendent des spécifications de tous ses composants.

Comprendre son architecture permet de savoir dans quelle mesure les caractéristiques spécifiques de chaque composant influencent la réactivité de la machine en fonction de son utilisation : pourquoi l'ajout de mémoire accélère-t-il l'ordinateur ? Pourquoi le temps d'accès d'un disque dur n'est-il qu'un des paramètres pour mesurer son efficacité ? Comment les processeurs vont-ils toujours plus vite ?

L'objectif principal de ce cours est de connaître les composants de base d'un ordinateur et de comprendre le schéma fonctionnel qui les relie. A la fin de ce cours, l'étudiant devra être capable de lister tous les composants de base d'un ordinateur. Il sera également apte à distinguer entre les fonctions de chaque composant. Aussi, il pourra facilement identifier la cause d'un problème de performance et proposer une solution matérielle appropriée.

#### Ce document est organisé comme suit :

Le chapitre 1 regroupe des notions générales sur la structure d'un ordinateur en présentant un petit historique sur l'évolution des ordinateurs depuis leurs apparition jusqu'aux modèles actuels. Ce chapitre aborde également la représentation de l'information dans un ordinateur et plus particulièrement le codage des nombres et l'arithmétique binaire.

Le chapitre 2 est un rappel des principes fondamentaux de la logique combinatoire et séquentielle, sur laquelle sont basés la plupart des composants de l'ordinateur.

Dans le chapitre 3, une brève description des mémoires est donnée pour permettre de bien comprendre la structure et le fonctionnement de la mémoire centrale d'un ordinateur.

Le quatrième et dernier chapitre aborde le composant maître de l'ordinateur à savoir le processeur. Ce chapitre décrit la structure interne du microprocesseur et les mécanismes de fonctionnement et de communication des différents composants.

#### Chapitre 1 : Généralités sur l'ordinateur

#### 1. Histoire des ordinateurs

L'ordinateur est né du travail de plusieurs ingénieurs et théoriciens pendant la Seconde Guerre mondiale. Il n'y avait pas un pôle de développement, mais plusieurs centres indépendants, chacun essayant de construire des machines qui n'existaient pas à l'époque. [1]

L'évolution de l'ordinateur actuel est passée par plusieurs étapes fortement liées aux inventions technologiques qui se distinguent en plusieurs générations. [2]

#### a. La génération zéro : les calculateurs mécaniques (Avant 1945)

- ► Les abaques (avant 1600):

- Instruments mécaniques facilitant le calcul

#### ► La Pascaline (1642):

- Inventée par Blaise Pascal.

- Machine qui additionne et soustrait les nombres de 6 chiffres en base 10.

- Les multiplication et divisions se faisaient par répétitions.

- Première machine à calculer!

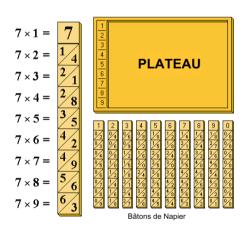

#### ► Le métier Jacquard (1805)

- Métier à tisser de Joseph Jacquard.

- Créé d'après des idées de Falcon en 1728.

- Système mécanique programmable.

- Utilise des cartes perforées pour métiers à tisser.

- C'est le 1er programme!

- ► La machine analytique de Charles Babbage (1833)

- Machine programmable.

- Capable de réaliser différentes opérations codées sur des cartes perforées.

- Dotée d'un dispositif d'entrées et sorties.

- Un organe de commande gérant le transfert des nombres et leur mise en ordre pour le traitement.

- Un magasin permettant de stocker les résultats intermédiaires ou finaux (mémoire).

- Un moulin chargée d'exécuter les opérations sur les nombres.

- Un dispositif d'impression.

#### b. La première génération : les tubes à vide (1945 - 1955)

- La Seconde Guerre Mondiale précipite l'avènement des ordinateurs.

- Les sous-marins allemands communiquaient par radio → interception facile.

- Les messages étaient chiffrés avec une machine ENIGMA, volée aux allemands.

- Besoin de beaucoup de calculs, rapidement pour les décrypter → Création du premier ordinateur électronique : le COLOSSUS.

1

- > Besoins de l'armée américaine pour le réglage des tirs d'artillerie.

- La course aux calculateurs est lancée à travers le monde!

#### Les tubes à vide :

- Également appelés tubes électroniques ou même lampes.

- C'est des amplificateurs de signal.

- Un ensemble d'électrodes placées dans le vide ou dans un gaz.

- C'est une source d'électrons.

- Remplacés plus tard par des semi-conducteurs.

# ► L'ENIAC de John Mauchly (1946):

- Electronic Numerical Integrator And Computer.

- 1<sup>er</sup> ordinateur électronique Turing-complet <sup>1</sup>.

- Calculs en système décimal.

- Composé de 18 000 tubes à vide et 1500 relais.

- 6000 commutateurs et une forêt de câbles.

- Pèse 30 tonnes, et occupe 167 m2.

- Incapable d'enregistrer un programme.

<sup>&</sup>lt;sup>1</sup> Turing-complet désigne en informatique un système formel ayant au moins le pouvoir des machines d'Alan Turing (machine universelle qui peut exécuter n'importe quel programme).

- ▶ L'EDSAC de von Neumann, Eckert et Mauchly (1946) :

- Basée sur l'ordinateur EDVAC (Electronic Discrete Variable Automatic Computer).

- Utilise un système binaire.

- Les opérations d'addition +, soustraction et multiplication × étaient automatiques.

- La division ÷ était programmable.

- Capacité mémoire initiale : 1000 mots de 44 bits.

#### c. La deuxième génération : les transistors (1955 - 1965)

- Le transistor a été inventé en 1948, aux Bell Labs (prix Nobel de Physique en 1956).

- Les ordinateurs à tubes à vide deviennent obsolètes à la fin des années 50's.

- Le MIT (Massachusetts Institute of Technology) est précurseur avec le TX-0.

- Les ordinateurs deviennent assez stables pour être vendus à des clients : naissance de l'industrie de la mini-informatique (IBM, DEC, HP, . . .).

- Premier jeu vidéo avec le PDP-1 : spacewar!

- Apparition des OS (Operating System) et langages évolués (FORTRAN et COBOL).

#### d. La troisième génération : les circuits intégrés (1965 - 1973)

- Le circuit intégré a été inventé en 1958.

- Des dizaines de transistors sur une seule puce.

- L'intégration a permis des ordinateurs plus petits, plus rapides et moins chers.

- Apparition de la multiprogrammation (plusieurs programmes exécutés en même temps sur la même machine).

- Possibilité d'émulation d'anciens modèles.

#### e. La quatrième génération : les microprocesseurs (1971 - 1980)

- Miniaturisation des circuits : l'ère de la micro-informatique

- Evolution de l'intégration avec la technologie VLSI (Very Large Scale Integration).

- Premier micro-processeur inventé par INTEL en 1971.

- Apparition des ordinateurs personnels (PC) utilisés pour :

- o Traitement de texte

- o Tableur

- Apparition d'Apple (1976)

#### f. Aujourd'hui: la loi de Moore<sup>2</sup> est encore d'actualité

Actuellement, les ordinateurs font partie intégrante de nos vies quotidiennes :

- Ordinateur jetable : Cartes de vœux

- Ordinateur enfoui : Montres, voitures

- Ordinateur de jeux : Jeux vidéo

- Ordinateur personnel (micro-ordinateur) : Ordinateurs portables ou de bureau

- Serveur : Serveurs de réseau

- Ensemble de stations de travail : Mini-superordinateur

- Mainframe: Traitement par lot dans une banque

- Superordinateur : Prévisions météo à long terme

#### 2. Structure de base d'un ordinateur

#### a. Définitions

Ordinateur : Machine capable de résoudre des problèmes en appliquant des instructions.

**Instruction**: Action à effectuer par l'ordinateur, correspondant à une étape dans un programme.

Programme: Suite d'instructions décrivant la façon dont l'ordinateur doit effectuer un travail.

Langage machine: Ensemble des instructions exécutables directement par un ordinateur.

<sup>&</sup>lt;sup>2</sup> Émise par l'ingénieur Gordon E. Moore en 1965, montrant l'évolution de la puissance de calcul des ordinateurs en fonction de la complexité du matériel informatique.

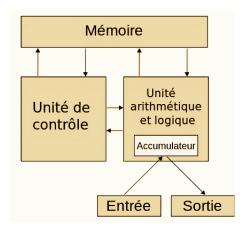

#### b. Architecture de John Von Neumann

Cette architecture est appelée ainsi en référence au mathématicien John von Neumann qui a élaboré en juin 1945 dans le cadre du projet EDVAC1 la première description d'un ordinateur dont le programme est stocké dans sa mémoire. [3]

La plupart des ordinateurs modernes utilisent cette architecture, seules les technologies ont changé.

Cette architecture est basée sur 4 parties principales :

- Unité arithmétique et logique (ALU) : effectue les opérations de base.

- Unité de contrôle : chargée du séquençage des opérations.

- **Mémoire** : contient les données et le programme

- Mémoire vive

- Mémoire de masse

- Entrées/Sorties : permettent de communiquer avec le monde extérieur.

Figure 1 : Schématisation de l'architecture de von Neumann. [4]

#### c. Architecture en couches

L'architecture matérielle et logicielle d'un ordinateur peut être représentée sous forme de couches superposées :

Niveau 5: Couche des langages d'application (langages haut niveau).

Niveau 4: Couche du langage d'assemblage.

Niveau 3 : Couche du système d'exploitation.

Niveau 2 : Couche architecture du jeu d'instructions (propre à chaque machine).

Niveau 1: Couche microarchitecture (UAL, opérations, registres, ...).

Niveau 0 : Couche logique numérique (circuits logiques).

#### d. L'ordinateur du point de vue interne

- Machine électronique binaire.

- Fonctionnement des composants de base : circuits électroniques

- Organisation et communication entre les composants

- Utilise un langage machine (système binaire).

- Munie d'un système d'exploitation :

- o Programme principal de l'ordinateur.

- o Permet l'exécution simultanée d'autres programmes.

- o Gère des périphériques : entrées/sorties, stockage.

Figure 2 : L'ordinateur du point de vue interne [2]

- 1. Ecran (Moniteur)

- 2. Carte mère

- **3.** CPU (Micro-processeur)

- **4.** Bus

- **5.** Mémoire vive (RAM)

- **6.** Cartes de périphériques

- 7. Alimentation

- **8.** Lecteur de disques

- 9. Disque Dur

- 10. Clavier

- 11. Souris

#### Kézako?!!

Annonce trouvée sur un site de vente en ligne :

Asus ET2210IUTS-B002E <sup>1</sup>, Microsoft Windows 7 Pro 64 bits <sup>2</sup>, Intel Core i3-2120 <sup>3</sup>, Multi-points Full HD <sup>4</sup>, 21.5" <sup>5</sup>, 1920 x 1080 <sup>6</sup>, Intel HD Graphics <sup>7</sup>, 1To <sup>8</sup>, 4096Mo <sup>9</sup>, DVD+/-RW Super Multi <sup>10</sup>, 1,3 M Pixel + Micro <sup>11</sup>, 2x 2W + Sonic Master DTS Surround Sensation UltraPC <sup>12</sup>, [1x Entrée HDMI, 1x Sortie HDMI, LAN port (RJ 45)] <sup>13</sup>, 802.11 b/g/n <sup>14</sup>, [2x ports USB 3.0, 3x ports USB 2.0] <sup>15</sup>, 590 x 461 x 60-230 mm <sup>16</sup>, 10.8kg <sup>17</sup>, Titane noir <sup>18</sup>

- 1. Référence modèle

- 2. Système d'exploitation

- 3. Processeur

- 4. Affichage

- 5. Taille écran (en pouces)

- 6. Résolution

- 7. Carte graphique

- 8. Disque dur

- 9. RAM

- 10. Lecteur de disques

- 11. Webcam

- 12. Enceintes

- 13. Connectiques

- 14. Wi-Fi

- 15. Ports USB

- 16. Taille de l'ensemble

- 17. Poids de l'ensemble

- 18. Couleur

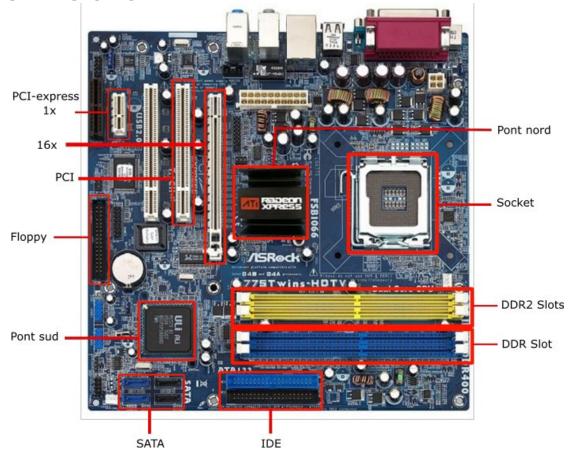

#### i. Carte mère

La carte mère est un circuit imprimé qui permet de mettre en contact physique les différents composants et périphériques.

Figure 3 : Composants de la carte mère [5]

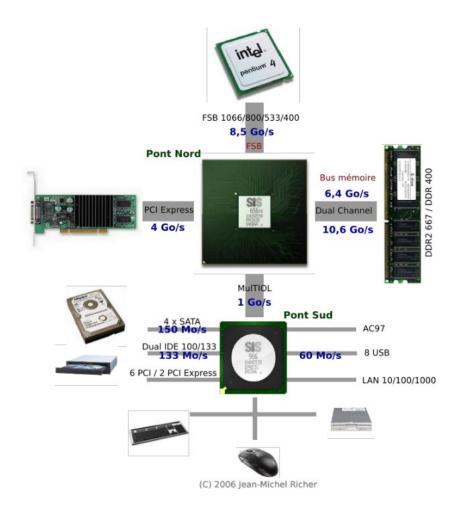

#### ii. Chipset

#### Composé de 2 parties :

Le pont nord (northbridge) : chargé de gérer les composants qui ont besoin d'une bande passante importante :

- microprocesseur

- mémoire vive (RAM)

- carte graphique

Le pont sud (southbridge) : chargé de gérer les périphériques qui ont besoin d'une faible bande passante :

- clavier, souris, audio

- port parallèle, port série

- périphériques USB, FireWire

- réseau

- disques durs, CD/DVD Rom

Figure 4 : Vue schématique d'une carte mère de type Intel avec chipset Sis 656fx/966, (2006) [5]

#### iii. Le Processeur

- En anglais CPU (Central Processing Unit) ou UC (Unité Centrale) en français.

- C'est le « Cerveau » de l'ordinateur.

- Exécute les programmes stockés en mémoire principale.

- Il est responsable du :

- Chargement des instructions

- Décodage des instructions

- o Exécution des instructions, l'une après l'autre

#### Il est composé de :

- Unité Arithmétique et Logique (UAL) :

- o En anglais ALU (Arithmetic and Logical Unit).

- O Responsable des opérations indiquées par les instructions.

#### • Unité de commande :

- O Récupère les instructions présentes en mémoire principale.

- Décode les instructions.

#### • Les registres :

- o Petites zones mémoires.

- O Peuvent être lus ou écrits extrêmement rapidement.

- Les bus : interconnectent les éléments fonctionnels internes.

- 1. L'Unité Arithmétique et Logique (UAL)

- Responsable des calculs sur des nombres entiers.

- Opérations communes :

- Opérations arithmétiques : addition, soustraction, changement de signe, . . .

- Opérations logiques : compléments, et, ou, ou-exclusif, non, non-et, . . .

- o Comparaisons : test d'égalité, supérieur, inférieur, . . .

- o Décalages : des bits à gauche, à droite...

#### 2. Les registres communs

- Compteur ordinal (CO) : contient l'adresse mémoire de l'instruction en cours d'exécution ou prochainement exécutée.

- Accumulateur (ACC): pour stocker les données en cours de traitement par l'UAL.

- Registre d'instructions (RI) : contient l'instruction en cours de traitement.

- Pointeur(s) de pile (SP): (Stack Pointer) contient l'adresse du sommet de la pile<sup>3</sup>.

- Registres généraux  $(R_0, ..., R_n)$ : registres de stockage intermédiaire pour les calculs.

#### 3. Exécution d'une instruction

L'exécution d'une instruction par le processeur passe par les étapes suivantes :

- 1) Charger la prochaine instruction à exécuter dans le registre instruction (RI).

- 2) Modifier le compteur ordinal (CO) pour qu'il pointe sur l'instruction suivante.

- 3) Décoder (analyser) l'instruction chargée.

- 4) Localiser en mémoire d'éventuelles données nécessaires à l'instruction.

- 5) Charger, si nécessaire, les données dans les registres généraux.

- 6) Exécuter l'instruction.

- 7) Recommencer à l'étape 1.

\_

<sup>&</sup>lt;sup>3</sup> Une pile est une zone de la mémoire gérée par le processeur selon le principe « dernier arrivé, premier sorti » (en anglais LIFO pour last in, first out).

#### iv. La Mémoire Principale

- Mémoire « de travail » de l'ordinateur.

- Mémoire vive : RAM (Random Access Memory)

- Caractéristiques :

- o Rapide d'accès.

- o Volatile.

- Le processeur y accède pour lire/écrire des données.

#### v. Les Entrées/Sorties

- En anglais « Input/Output » (I/O)

- Permettent les échanges d'information entre le processeur et les périphériques associés.

- Entrées : données envoyées par un périphérique à destination du processeur.

- Sorties : données émises par le processeur à destination des périphériques.

- 1. Les périphériques d'entrée :

Permettent à l'utilisateur de fournir une information à l'ordinateur.

- ► Exemples : clavier, scanner, . . .

- 2. Les périphériques de sortie :

Permettent à l'ordinateur de fournir une information à l'utilisateur

- ► Exemples : écran, enceintes, . . .

- 3. Les périphériques d'entrée-sortie :

Permettent à l'utilisateur/l'ordinateur de fournir/recevoir une information

- ► Exemples : clé USB, . . .

- ▶ Quelques exemples de périphériques :

| Périphérique   | Entrée | Sortie | Entrée/Sortie |

|----------------|--------|--------|---------------|

| Clavier        | •      |        |               |

| Souris         | •      |        |               |

| Ecran          |        | •      |               |

| Ecran tactile  |        |        | •             |

| Lecteur CD/DVD | •      |        |               |

| Graveur CD/DVD |        |        | •             |

| Webcam         | •      |        |               |

| Imprimante     |        | •      |               |

| Carte réseau   |        |        | •             |

| Microphone     | •      |        |               |

| Enceinte       |        | •      |               |

| Scanner        | •      |        |               |

| Disque dur     |        |        | •             |

| Clé USB        |        |        | •             |

#### vi. Les bus

- Canaux de communication à l'intérieur de l'ordinateur.

- Relient les différents composants de l'ordinateur.

- Caractérisés par :

- o Un type : parallèle ou série.

- o Une largeur : nombre de bits que le bus peut transmettre à la fois.

- o Une fréquence (vitesse) : nombre de paquets envoyées par seconde (en Hz).

- o Une bande passante (débit) = largeur × fréquence.

#### Il y a 3 types de bus:

- **Bus de données** : définit la taille des données pour les E/S

- Bus d'adresse : permet l'adressage de la mémoire

- Bus de contrôle : permet la gestion du matériel, via les interruptions

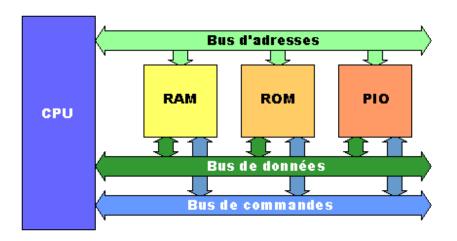

Figure 5 : Schéma des bus de communication [5]

#### ► La connectique :

Les composants de l'unité centrales sont connectés à la carte mère via des ports spécifiques.

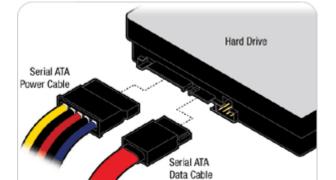

• Ports pour disques dur et lecteurs CD/DVD :

Ports SATA

• Ports pour cartes additionnelles : (cartes graphique, carte son, carte TV...)

#### Port PCI

Port AGP

• Socket: pour brancher le microprocesseur.

• Ports USB: Universal Serial Bus

#### 3. Représentation et codage de l'information

Les informations traitées par les ordinateurs sont de différentes natures :

- Nombres, texte,

- Images, sons, vidéo,

- Programmes, ...

- Dans un ordinateur, elles sont toujours représentées sous forme binaire (BIT : Binary digIT)

- Une suite de 0 et de 1.

#### a. Codage de l'information

Le codage de l'information permet d'établir une correspondance qui permet sans ambiguïté de passer d'une représentation (dite externe) d'une information à une autre représentation (dite interne : sous forme binaire) de la même information, suivant un ensemble de règles précises.

#### Exemple:

- Le nombre 35 : 35 est la représentation externe du nombre trente-cinq.

- La représentation interne de 35 sera une suite de 0 et 1 (100011).

En informatique, Le codage de l'information s'effectue principalement en trois étapes :

- 1. L'information sera exprimée par une suite de nombres (Numérisation).

- 2. Chaque nombre est codé sous forme binaire (suite de 0 et 1).

- 3. Chaque élément binaire est représenté par un état physique.

Le codage de l'élément binaire par un état physique peut se faire par :

- Charge électrique (RAM : Condensateur-transistor) : Chargé (bit 1) ou non chargé (bit 0)

- Magnétisation (Disque dur, disquette) : polarisation Nord (bit 1) ou Sud (bit 0)

- Alvéoles (CDROM) : réflexion (bit 1) ou pas de réflexion (bit 0)

- Fréquences (Modem) : dans un signal sinusoïdal.

#### b. Système de numération

Système de numération décrit la façon avec laquelle les nombres sont représentés.

Un système de numération est défini par :

- Un alphabet A: ensemble de symboles ou chiffres,

- Des règles d'écritures des nombres : juxtaposition de symboles.

- i. Exemples de Système de numération

- Numération Romaine : I, II, III, IV, ..., X, ..., CCLXXI -> 271

- Numération babylonienne : I , II , III , T , II ,..., T & T

- Numération décimale :  $A = \{0,1,2,3,4,5,6,7,8,9\}$

- O Le nombre 10 est la base de cette numération

- o C'est un système positionnel. Chaque position possède un poids.

#### ii. Système de numération positionnel pondéré à base b

Un système de numérotation positionnel pondéré à base b est défini sur un alphabet de b chiffres:

$$A = \{c_0, c_1, ..., c_{b-1}\}$$

avec  $0 \le c_i < b$

- Soit  $N = a_{n-1} a_{n-2} ... a_1 a_{0 (b)}$ : représentation en base b sur n chiffres.

- o a<sub>i</sub>: est un chiffre de l'alphabet de poids i (position i).

- o a<sub>0</sub> : chiffre de poids 0 appelé le chiffre de poids faible.

- o a<sub>n-1</sub>: chiffre de poids n-1 appelé le chiffre de poids fort.

- La valeur de N en base 10 est donnée par :

$$N = a_{n-1}.b^{n-1} + a_{n-2}.b^{n-2} + ... + a_0.b^0{}_{(10)} = \sum_{i=0}^{n-1} a_i .b^i$$

#### iii. Bases de numération

- **Système binaire :** système à base 2 (b=2) utilise deux chiffres : {0,1}

- o C'est avec ce système que fonctionnent les ordinateurs

- Système Octal: système à base 8 (b=8) utilise huit chiffres: {0,1,2,3,4,5,6,7}

- O Utilisé il y a un certain temps en Informatique.

- o Elle permet de coder **3 bits** par un seul symbole.

- Système Hexadécimal: système à base 16 (b=16) utilise 16 chiffres:

$$\{0,1,2,3,4,5,6,7,8,9, A=10_{(10)}, B=11_{(10)}, C=12_{(10)}, D=13_{(10)}, E=14_{(10)}, F=15_{(10)}\}$$

- O Cette base est très utilisée dans le monde de la micro-informatique.

- o Elle permet de coder 4 bits par un seul symbole.

#### iv. Transcodage (conversion de base)

Le transcodage ou conversion de base est l'opération qui permet de passer de la représentation d'un nombre exprimé dans une base à la représentation du même nombre mais exprimé dans une autre base.

Par la suite, on verra les conversions suivantes :

- Décimal vers Binaire, Octal et Hexadécimal.

- Binaire vers Décimal, Octale et Hexadécimal.

#### 1. De la base 10 vers une base b

La règle à suivre est les divisions successives :

- On divise le nombre par la base b.

- Puis le quotient par la base b.

- Ainsi de suite jusqu'à l'obtention d'un quotient nul.

- La suite des restes correspond aux symboles de la base visée.

- On obtient en premier le chiffre de poids faible et en dernier le chiffre de poids fort.

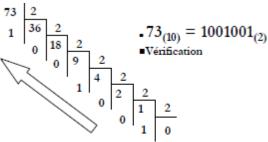

Exemple : Soit N le nombre d'étudiants d'une classe représenté en base décimale par : N = 73<sub>(10)</sub>

Représentation en Binaire ?

Représentation en Octal?

Représentation en Hexadécimal?

$$73 | 16 \\ 9 | 4 | 16 \\ 0$$

$73_{(10)} = 49_{(16)}$

• Vérification

- 2. De la base 2 vers une base b

- **Solution 1** : convertir le nombre en base binaire vers la base décimale puis convertir ce nombre en base 10 vers la base b.

- o Exemple:

$$10010_{(2)} = ?_{(8)} 10010_{(2)} = 2^4 + 2^1_{(10)} = 18_{(10)} = 2*8^1 + 2*8^0_{(10)} = 22_{(8)}$$

- Solution 2:

- O Binaire vers décimal : par définition  $(\sum_{i=0}^{n-1} a_i . b^i)$

- **Exemple**: Soit N =  $1010011101_{(2)}$  = ? (10) N =  $1 \times 2^9 + 0 \times 2^8 + 1 \times 2^7 + 0 \times 2^6 + 0 \times 2^5 + 1 \times 2^4 + 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$ = 512 + 0 + 128 + 0 + 0 + 16 + 8 + 4 + 0 + 1=  $669_{(10)}$

- $\Rightarrow$  1010011101<sub>(2)</sub>=669<sub>(10)</sub>

- O Binaire vers octal: regroupement des bits en des sous-ensembles de trois bits puis remplacer chaque groupe par le symbole correspondant dans la base 8. (Voir tableau ci-contre)

- **Exemple** : Soit  $N = 1010011101_{(2)} = ?_{(8)}$

$$N = 001 \ 010 \ 011 \ 101_{(2)} \\

= 1 \ 2 \ 3 \ 5_{(8)}$$

$\Rightarrow$  1010011101<sub>(2)</sub>= 1235<sub>(8)</sub>

| Symbole | Suite   |

|---------|---------|

| Octale  | binaire |

| 0       | 000     |

| 1       | 001     |

| 2       | 010     |

| 3       | 011     |

| 4       | 100     |

| 5       | 101     |

| 6       | 110     |

| 7       | 111     |

|         |         |

Binaire vers Hexadécimal : regroupement des bits en des sous-ensembles de quatre bits puis remplacer chaque groupe par le symbole correspondant dans la base 16. (Voir tableau ci-contre).

|   | Ex | emp | le : S | oit $N = 1010011101_{(2)} = ?_{(16)}$ |

|---|----|-----|--------|---------------------------------------|

| N | =0 | 010 | 1001   | 1101(2)                               |

|   | =  | 2   | 9      | D <sub>(16)</sub>                     |

| $\Rightarrow$ 1010011101 <sub>(2)</sub> = 29D <sub>(16)</sub> |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Symbole     | Suite   |

|-------------|---------|

| Hexadécimal | binaire |

| 0           | 0000    |

| 1           | 0001    |

| 2           | 0010    |

| 3           | 0011    |

| 4           | 0100    |

| 5           | 0101    |

| 6           | 0110    |

| 7           | 0111    |

| 8           | 1000    |

| 9           | 1001    |

| A           | 1010    |

| В           | 1011    |

| С           | 1100    |

| D           | 1101    |

| Е           | 1110    |

| F           | 1111    |

#### c. Codage des nombres

- i. Codage des entiers naturels

- 1. Utilisation du code binaire pur :

- o L'entier naturel (positif ou nul) est représenté en base 2,

- o Les bits sont rangés selon leur poids, on complète à gauche par des 0.

- Exemple: sur un octet,  $10_{(10)}$  se code en binaire pur:  $0\ 0\ 0\ 1\ 0\ 1\ 0_{(2)}$

- **2.** Etendu du codage binaire pur :

- o Sur n bits on peut coder des nombres de 0 à 2<sup>n</sup> − 1

- O Sur 1 octet (8 bits): codage des nombres de 0 à  $2^8$  1 = 255

- O Sur 2 octets (16 bits): codage des nombres de 0 à  $2^{16}$  1 = 65535

- Sur 4 octets (32 bits) : codage des nombres de 0 à  $2^{32}$  1 = 4 294 967 295

- **3.** Arithmétique en base 2

- o Les opérations sur les entiers s'appuient sur des tables d'addition et de multiplication:

Addition

| 0 | 0 | 0                       |

|---|---|-------------------------|

| 0 | 1 | 1                       |

| 1 | 0 | 1                       |

| 1 | 1 | <sup>(1)</sup> <b>0</b> |

| 1 | 1 |                         |

Retenue

#### Multiplication

| 0 | 0 | 0 |

|---|---|---|

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

► Exemple (Addition)

Addition binaire (8 bits) 10010110

> $+\;0\;1\;0\;1\;0\;1\;0\;1$ 11101011

Addition binaire (8 bits) avec (débordement ou overflow):

> 10010110 +01110101100001011

> > *⇒ Overflow*

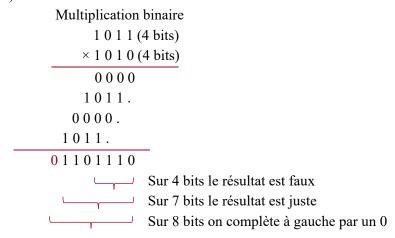

#### ► Exemple (Multiplication)

#### ii. Codage des entiers relatifs

Il existe au moins trois façons pour coder un entier relatif (signé):

- Code binaire signé (par signe et valeur absolue).

- Code complément à 1.

- Code complément à 2 (utilisé sur ordinateur).

- 1. Binaire signé

- Le bit le plus significatif est utilisé pour représenter le signe du nombre :

- Si le bit le plus fort = 1 alors nombre négatif

- Si le bit le plus fort = 0 alors nombre positif

- Les autres bits codent la valeur absolue du nombre.

- ► Exemple : Sur 8 bits, codage des nombres -24 et -128 en (bs)

- -24 est codé en binaire signé par : 1 0 0 1 1 0 0 0<sub>(bs)</sub>

- -128 hors limite nécessite 9 bits au minimum.

- Etendu de codage :

- Avec n bits, on code tous les nombres entre  $-(2^{n-1}-1)$  et  $(2^{n-1}-1)$ .

- Avec 4 bits : -7 et +7.

- ➤ Limitations du binaire signé :

- Deux représentations du zéro : +0 et -0

- Sur 4 bits:  $+0 = 0000_{(bs)}$ ,  $-0 = 1000_{(bs)}$

- Multiplication et l'addition sont moins évidentes.

- 2. Code complément à 1

Aussi appelé Complément Logique (CL) ou Complément Restreint (CR) :

- Les nombres positifs sont codés de la même façon qu'en binaire pur.

- Un nombre négatif est codé en **inversant** chaque bit de la représentation de sa valeur absolue.

- Le bit le plus significatif est utilisé pour représenter le signe du nombre :

- Si le bit le plus fort = 1 alors nombre négatif.

- Si le bit le plus fort = 0 alors nombre positif.

- ► Exemple : -24 en complément à 1 sur 8 bits |-24| en binaire pur ⇒ 0 0 0 1 1 0 0 0 (2), puis on inverse les bits ⇒ 1 1 1 0 0 1 1 1 (cà1)

- Limitations du complément à 1 :

- Deux codages différents pour 0 (+0 et -0)

- Sur 8 bits:  $+0 = 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0_{(cal)}$  et  $-0 = 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1_{(cal)}$

- Multiplication et l'addition sont moins évidentes.

- 3. Code complément a 2

#### Aussi appelé Complément Vrai (CV) :

- Les nombres positifs sont codés de la même manière qu'en binaire pur.

- Un nombre négatif est codé en ajoutant la valeur 1 à son complément à 1.

- Le bit le plus significatif est utilisé pour représenter le signe du nombre.

- Exemple : -24 en complément à 2 sur 8 bits

24 est codé par 0 0 0 1 1 0 0 0<sub>(2)</sub>

-24 ⇒ 1 1 1 0 0 1 1 1<sub>(cà1)</sub>, puis on lui additionne 1 donc -24 est codé par 1 1 1 0 1 0 0 0<sub>(cà2)</sub>

- > Un seul codage pour 0. Par exemple sur 8 bits :

- +0 est codé par 0000000<sub>(cà2)</sub>

- -0 est codé par  $11111111_{(cal)} \Rightarrow donc$  -0 sera représenté par  $0000000_{(cal)}$

- Etendu de codage :

- Avec n bits, on peut coder de  $-(2^{n}-1)$  à  $(2^{n-1}-1)$

- Sur 1 octet (8 bits), codage des nombres de -128 à 127

```

\circ +0 = 00000000 -0 = 00000000

\circ +1 = 00000001 -1 = 111111111

\circ +127 = 01111111 -128 = 10000000

```

#### iii. Codage des nombres réels

Les formats de représentations des nombres réels sont :

- Format virgule fixe : (utilisé par les premières machines)

- O Possède une partie « entière » et une partie « décimale » séparés par une virgule.

- O La position de la virgule est fixe d'où le nom.

- $\triangleright$  Exemple: 54,25<sub>(10)</sub>; 10,001<sub>(2)</sub>; A1,F0B<sub>(16)</sub>

- Format virgule flottante : (utilisé actuellement sur machine)

- $\circ$  Défini par :  $\pm \mathbf{m} \cdot \mathbf{b}^{e}$

- un signe + ou –

- une mantisse **m** (en virgule fixe)

- un exposant e (un entier relative)

- une base **b** (2,8,10,16,...)

- Exemple:  $0.5425 \cdot 10^{2}_{(10)}$ ;  $10.1 \cdot 2^{-1}_{(2)}$ ; A0,B4. $16^{-2}_{(16)}$

#### 1. Codage en Virgule Fixe

Etant donné une base b, un nombre X est représenté, en format virgule fixe, par :

- $X = a_{n-1} a_{n-2} \dots a_1 a_0, a_{-1} a_{-2} \dots a_{-p (b)}$

- a<sub>n-1</sub> est le chiffre de poids fort (MSB<sup>4</sup>).

- a<sub>-p</sub> est le chiffre de poids faible (LSB<sup>5</sup>).

- n est le nombre de chiffre avant la virgule.

- p est le nombre de chiffre après la virgule.

- La valeur de X en base 10 est :  $X = \sum_{i=0}^{n-1} a_i \cdot b^i$

- Exemple:  $101,01_{(2)} = 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2} = 5,25_{(10)}$

- ✓ Changement de base  $10 \rightarrow 2$

- Le passage de la base 10 à la base 2 est défini par :

- O Une partie entière codée sur p bits (division successive par 2)

- O Une partie décimale codée sur q bits en multipliant par 2 successivement jusqu'à ce que la partie décimale soit nulle ou le nombre de bits q est atteint.

- Exemple:  $4,25_{(10)} = ?_{(2) \text{ format virgule fixe}}$   $4_{(10)} = 100_{(2)}$   $0,25 \times 2 = 0,5 \rightarrow 0$   $0,5 \times 2 = 1,0 \rightarrow 1$  $\Rightarrow \text{donc } 4,25_{(10)} = 100,01_{(2)}$

#### 2. Codage en Virgule Flottante

Un nombre réel est représenté en virgule flottante sous la forme :  $\pm$  M × 2 <sup>E</sup>, où M est la mantisse (virgule fixe) et E l'exposant (signé). Coder en base 2 au format virgule flottante, revient à coder le signe, la mantisse et l'exposant.

▶ Exemple : Codage en base 2, format virgule flottante, du nombre 3,25

```

3,25_{(10)} = 11,01_{(2)} (en virgule fixe)

= 1,101 \times 2^{1}_{(2)} \rightarrow on décale la virgule par 1 bit à gauche.

= 110,1 \times 2^{-1}_{(2)} \rightarrow on décale la virgule par 1 bit à droite.

```

Problème : il y a différentes manières de représenter E et M.

- $\Rightarrow$  **Normalisation**: afin d'avoir la même représentation, tout nombre doit d'abord être normalisé sous la forme :  $\pm$  1,M  $\times$  2<sup>Eb</sup>

- Le signe est codé sur 1 bit ayant le poids fort (S):

- o Le signe : bit 1

- o Le signe + : bit 0

<sup>&</sup>lt;sup>4</sup> Most significant bit

<sup>&</sup>lt;sup>5</sup> Less significant bit

- Exposant biaisé (**Eb**):

- O Placé avant la mantisse pour simplifier la comparaison.

- Codé sur p bits et biaisé pour être positif (ajout de 2<sup>p-1</sup>-1).

- Mantisse normalisée (**M**):

- Normalisée : la virgule est placée après le bit à 1 ayant le poids fort.

- o M est codé sur q bits

- Exemple:  $11,01 \Rightarrow 1,101 \times 2^1$  donc M = 101

| S    | Eb     | M      |

|------|--------|--------|

| 1bit | p bits | q bits |

#### > Standard IEEE 754 (1985)

C'est la norme la plus employée actuellement pour le calcul des nombres à virgule flottante avec les CPU. Elle définit les nombres réels sur les formats :

- Simple précision, codé sur 32 bits :

- o 1 bit de signe (S).

- o 8 bits pour l'exposant biaisé (Eb).

- o 23 bits pour la mantisse (M).

| S    | Eb     | M       |

|------|--------|---------|

| 1bit | 8 bits | 23 bits |

- **Double précision**, codé sur 64 bits :

- o 1 bit de signe (S).

- o 11 bits pour l'exposant biaisé (**Eb**).

- o 52 bits pour la mantisse (M).

| S    | Eb      | M       |

|------|---------|---------|

| 1bit | 11 bits | 52 bits |

► Conversion décimale - IEEE754 (Codage d'un réel)

► Conversion IEEE754 – Décimale (Evaluation d'un réel)

#### Caractéristiques des nombres flottants au standard IEEE

|                             | Simple précision          | Double précision           |

|-----------------------------|---------------------------|----------------------------|

| Bit de signe                | 1                         | 1                          |

| Bits d'exposant             | 8                         | 11                         |

| Bits de mantisse            | 23                        | 52                         |

| Nombre total de bits        | 32                        | 64                         |

| Codage de l'exposant        | Excédant 127              | Excédant 1023              |

| Variation de l'exposant     | -126 à +127               | -1022 à +1023              |

| Plus petit nombre normalisé | 2-126                     | 2-1022                     |

| Plus grand nombre normalisé | Environ 2 <sup>+128</sup> | Environ 2 <sup>+1024</sup> |

#### d. Codage des caractères

Les caractères peuvent être soit Alphabétique (A-Z, a-z), soit numérique (0, ..., 9), des signes de ponctuation, ou des caractères spéciaux (&, \$, %, ...). Le codage des caractères revient à créer une table de correspondance entre les caractères et des nombres.

#### Les Standards:

- Code (ou Table) **ASCII** (American Standard Code for Information Interchange):

- o 7 bits pour représenter 128 caractères (0 à 127)

- o 48 à 57 : chiffres dans l'ordre (0, 1, ..., 9)

- o 65 à 90 : les alphabets majuscules (A, ..., Z)

- o 97 à 122 : les alphabets minuscule (a, ..., z)

#### • Code **ASCII Etendu**:

- o 8 bits pour représenter 256 caractères (0 à 255)

- O Code les caractères accentués : à, é, è, ...etc.

- o Compatible avec ASCII.

- Code Unicode (mis au point en 1991)

- 16 bits pour représenter 65 536 caractères (0 à 65 535).

- o Compatible avec ASCII.

- Code la plupart des alphabets : Arabe,

Chinois, ...etc.

- On en a défini environ 50 000 caractères pour l'instant.

|     | MSB  | 8    | 9    | Α    | В    | С    | D    | Е    | F    |

|-----|------|------|------|------|------|------|------|------|------|

| LSB |      | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| 0   | 0000 | ç    | Ė    | á    | - 5  | L    | 8    | Ó    | -    |

| 1   | 0001 | ü    | 39   | - 1  | 8    |      | Ð    |      | ±    |

| 2   | 0010 | 6    | Æ    | Ó    | Ħ    | т    | Ê    | - 6  | _    |

| 3   | 0011 | â    | 6    | ú    |      | H    | E    | ò    | %    |

| 4   | 0100 | ä    | ő    | ń    | 4    | -    | Ê    | ő    | 1    |

| - 5 | 0101 | à    | ò    | Ń    | A    | +    | 1    | Ő    | - 6  |

| -6  | 0110 | 5    | û    | 0    | Â    | - 5  | - (  | μ    | +    |

| 7   | 0111 | ç    | ù    | •    | À    | Á    | î    | ⊳    | ,    |

| 8   | 1000 | ê    | 9    | 6    | 0    | Ŀ    | 1    | Þ    | 0    |

| 9   | 1001 | 9    | Ó    | 0    | 4    | F    | 7    | Û    | -    |

| A   | 1010 | è    | 0    |      |      | Ŧ    | г    | 0    | -    |

| В   | 1011 | T    | ō    | %    | 7    | Ŧ    |      | Û    | -1   |

| C   | 1100 | î    | £    | -9/4 | 4    | ŀ    | -    | ý    | e    |

| D   | 1101 | ì    | Ø    | ;    | ¢    | =    | 1    | Ý    | z    |

| Е   | 1110 | Ã    | ×    | - 60 | ¥    | ÷    | ì    | -    | •    |

| F   | 1111 | A    | 1    |      | ٦    | ж    | •    | - 1  |      |

|   | FE7    | FE8  | FE9              | FEA       | FEB  | FDF          |

|---|--------|------|------------------|-----------|------|--------------|

| 0 | "      | ۶    | ·                | ج         | ;    | صلے          |

|   | FE70   | FE80 | FE90             | FEA0      | FEB0 | FDF0         |

| 1 | -      | T    | :                | ح         | س    | قلے          |

|   | FE71   | FE81 | FE91             | FEA1      | FEB1 | FDF1         |

| 2 | € FE72 |      | FE92             | FEA2      | FEB2 | الله<br>FDF2 |

| 3 | FE73   | FE83 | <b>5</b><br>FE93 | ><br>FEA3 | FEB3 | آکبر<br>FDF3 |

|   | FE/3   | LE09 | FE93             | FEAS      | LEDS | 1013         |

| 4 | ×      | ٲ    | ä                | *         |      | خُصِّکُ      |

|   | FE74   | FE84 | FE94             | FEA4      | FEB4 | FDF4         |

|   |        |      |                  |           |      | •            |

#### e. Codage d'une image

Le principe du codage d'une image :

- Tout commence par découper l'image en des petits carrés c'est en quelque sorte poser une grille (aussi serrée que possible) sur l'image.

- Deux nombres seront importants pour décrire cette grille : le nombre de petits carrés en largeur et ce même nombre en hauteur.

- Plus ces nombres sont élevés, plus la surface de chaque petit carré est petite et plus le dessin tramé sera proche de l'originale.

On obtient donc pour toute l'image un quadrillage comme celui montré ci-dessous pour une partie.

Il ne reste plus qu'à en déduire une longue liste d'entiers :

- Le nombre de carré sur la largeur.

- Le nombre de carré sur la hauteur.

- Suite de nombres pour coder l'information (Couleur) contenue dans chaque petit carré qu'on appelle pixel (PICture ELement):

- o Image en noir et blanc  $\rightarrow$  1 bit pour chaque pixel.

- o Image avec 256 couleurs  $\rightarrow$  1 octet (8 bits) pour chaque pixel.

- o Image en couleur vrai (True Color : 16 millions de couleurs) → 3 octets (24 bits) pour chaque pixel.

La manière de coder un dessin en série de nombres s'appelle une représentation BITMAP.

L'infographie est le domaine de l'informatique concernant la création et la manipulation des images numériques.

La **définition**: détermine le nombre de pixel constituant l'image. Une image possédant 800 pixels en largeur et 600 pixels en hauteur aura une définition notée 800x600 pixels.

La **profondeur** ou la dynamique d'une image est le nombre de bits utilisé pour coder la couleur de chaque pixel.

Le **poids** d'une image (exprimé en Ko ou en Mo) : est égal à son nombre de pixels (définition) que multiplie le poids de chacun des pixels (profondeur).

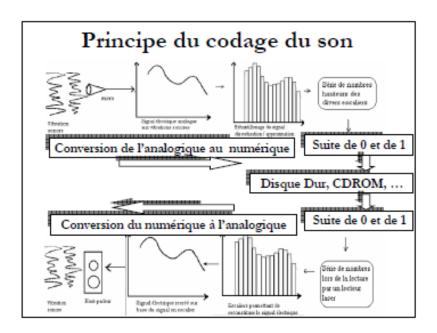

#### f. Codage du son

Un son est une vibration mécanique se propageant dans l'air ou dans un autre milieu (fluide, solide...). Lors de la numération, il faut transformer le signal analogique (continu) en une suite de nombres qui seront traités par l'ordinateur. C'est le rôle du convertisseur analogique/numérique.

La numérisation d'un son se réalise en deux étapes :

- L'échantillonnage : consiste à prélever périodiquement des échantillons d'un signal analogique selon une période que l'on appellera période d'échantillonnage.

- La quantification : consiste à affecter une valeur numérique à chaque échantillon prélevé.

Les Codecs, abréviation de codeur/décodeur, sont des logiciels qui permettent de réaliser ce codage/décodage du son dans un ordinateur. Ces logiciels s'appuient sur les éléments matériels disponibles dans la carte son.

#### **Exercices**

#### Série de TD N°1

(Comptage binaire)

#### **Exercice 1 : (Conversion de bases)**

Exprimez le nombre décimal 100 dans toutes les bases de 2 à 9 et en base 16.

#### **Exercice 2 : (Représentation des entiers)**

Exprimez les nombres décimaux 94, 141, 163 et 197 en base 2, 8 et 16. Donnez sur 8 bits les représentations « binaire signé », complément à 1 et complément à 2 des nombres décimaux 45, 73, 84, –99, –102 et –118.

#### **Exercice 3 : (Calcul binaire)**

- 1/ Effectuez la soustraction 122 43 dans la représentation en complément à 2 en n'utilisant que l'addition.

- 2/ Multipliez les nombres binaires 10111 et 1011 ; vérifiez le résultat en décimal.

#### **Exercice 4 : (Représentation des réels - virgule fixe)**

- 1/ Coder en virgule fixe au format Q8.8 les nombres suivants : 23.375, 100, 365.2, -54.65.

- 2/ Décoder le nombre 6C60<sub>(16)</sub> en virgule fixe dans le format Q10.6.

- 3/ Décoder le nombre D7EA (16) en virgule fixe dans le format Q8.8.

- 4/ Déterminer le nombre maximum représentable en virgule fixe sur le format Q4.4.

- 5/ Déterminer le nombre minimal strictement positif représentable sur ce même format.

- 6/ Déterminer le pas de ce format.

#### **Exercice 5 : (Virgule flottante - Norme IEEE754)**

Soit une machine où les nombres réels sont représentés sous la forme ( $\pm$  1,M .  $2^{Eb}$ ) sur 32 bits, numérotés de droite à gauche de 0 à 31 avec :

- Une pseudo-mantisse M normalisée sur 23 bits (les bits 0 à 22).

- Un exposant biaisé, représentant une puissance de 2, codé sur 8 bits (les bits 23 à 3).

- Un bit pour le signe de la mantisse (le bit 31).

- 1/ Déterminer le nombre maximum représentable dans ce format.

- 2/ Déterminer le nombre minimal strictement positif représentable dans ce même format.

- 3/ Donner en octal, la représentation IEEE754 correspondant au nombre décimal -32,625.

- 4/ Mettre sous le format *IEE*754, les deux nombres AE8<sub>(16)</sub> et 9D0<sub>(16)</sub> puis calculer leur valeur décimale.

#### Chapitre 2 : Logique combinatoire et séquentielle

L'analyse des circuits logiques nécessite l'utilisation d'une algèbre spécifique, dite « booléenne », fruit des travaux du mathématicien anglais George Boole du 19ème siècle. Ces travaux ont défini un ensemble d'opérateurs de base, ainsi que leurs propriétés, qui constituent une algèbre permettant de concevoir tout type de circuit. La construction de fonctions logiques répondant à des contraintes précises et leur représentation sous forme de circuits électroniques est réalisée par des opérateurs élémentaires. [1]

Alors qu'en algèbre classique, les variables et les fonctions peuvent prendre n'importe quelle valeur, ici elles sont limitées aux valeurs 0 et 1. Une fonction de n variables booléennes sera définie à partir de {0. 1} nà {0, 1}. Il est également complètement défini par les valeurs qu'il suppose dans les 2<sup>n</sup> combinaisons possibles de ses variables d'entrée, comme chaque valeur de fonction ne peut être que 0 ou 1, il existe 2<sup>2<sup>n</sup></sup> fonctions différentes de n variables. On peut donc décrire une fonction donnée (avec n variables) en expliquant ses 2<sup>n</sup> valeurs, par exemple, à partir de sa table de vérité. Il s'agit d'un tableau de 2<sup>n</sup> lignes, qui répertorie pour chaque combinaison possible de variables d'entrée (une ligne) la valeur assumée par la fonction.

#### 1. Circuits logiques

Un circuit logique est un Circuit dans lequel seules 2 valeurs logiques sont possibles : 0 ou 1. Il est réalisé par un circuit électrique (transistors) :

- Une faible tension représente la valeur binaire 0.

- Une tension élevée représente 1.

Les composants de base d'un circuit logique sont : les **portes logiques**.

#### ▶ Porte logique :

- Permet de combiner les signaux binaires.

- Reçoit en entrée une ou plusieurs valeurs binaires (souvent 2).

- Renvoie une unique valeur binaire en sortie.

#### a. Fonctions logiques élémentaires

#### i. Fonction NON (NOT)

- Si la valeur d'entré est 1, alors la sortie vaut 0.

- Si la valeur d'entrée est 0, alors la sortie vaut 1.

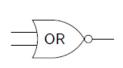

#### ii. Fonction OU (OR)

| a | b | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$$S = f(a,b) = a+b$$

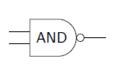

#### iii. Fonction ET (AND)

| a | b | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$S = f(a,b) = a \times b = ab$$

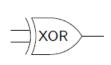

#### iv. Fonction OU-exclusif (XOR)

| a | b | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$$S = f(a,b) = a \oplus b$$

$$= (a+b)(\overline{ab})$$

$$= (a+b)(\bar{a}+\bar{b})$$

$$= a\bar{a} + a\bar{b} + b\bar{a} + b\bar{b}$$

$$= a\bar{b} + b\bar{a}$$

$$= \overline{a\bar{b}} + \overline{b\bar{a}}$$

$$= \overline{a\bar{b}} + \overline{b\bar{a}}$$

$$= \overline{a\bar{b}} + \overline{b\bar{a}}$$

#### v. Fonction NON-OU (NOR)

| a | b | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

$$S = f(a,b) = \overline{a+b}$$

#### vi. Fonction NON-ET (NAND)

| a | b | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$$S = f(a,b) = \overline{a.b} = \overline{ab}$$

#### ► Exemple des fonctions booléennes de 2 variables :

| f(a,b)          | 00 | 01 | 10 | 11 |

|-----------------|----|----|----|----|

| 0               | 0  | 0  | 0  | 0  |

| ab              | 0  | 0  | 0  | 1  |

| $a\overline{b}$ | 0  | 0  | 1  | 0  |

| а               | 0  | 0  | 1  | 1  |

| āb              | 0  | 1  | 0  | 0  |

| b               | 0  | 1  | 0  | 1  |

| a⊕b             | 0  | 1  | 1  | 0  |

| a+b             | 0  | 1  | 1  | 1  |

| f(a,b)                  | 00 | 01 | 10 | 11 |

|-------------------------|----|----|----|----|

| $\overline{a+b}$        | 1  | 0  | 0  | 0  |

| $\overline{a \oplus b}$ | 1  | 0  | 0  | 1  |

| $\bar{b}$               | 1  | 0  | 1  | 0  |

| $a + \overline{b}$      | 1  | 0  | 1  | 1  |

| ā                       | 1  | 1  | 0  | 0  |

| $\bar{a} + b$           | 1  | 1  | 0  | 1  |

| $\overline{ab}$         | 1  | 1  | 1  | 0  |

| 1                       | 1  | 1  | 1  | 1  |

#### b. Règles de calcul

| Commutativité                                                                                                                                         | Associativité                                                                                                                       | Distributivité                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $a + b = b + a$ $ab = ba$ $a \oplus b = b \oplus a$                                                                                                   | $a + (b + c) = (a + b) + c = a + b + c$ $a(bc) = (ab)c = abc$ $a \oplus (b \oplus c) = (a \oplus b) \oplus c = a \oplus b \oplus c$ | $a + (bc) = (a+b)(a+c)$ $a(b+c) = (ab) + (ac) = ab + ac$ $a(b\oplus c) = (ab)\oplus (ac) = ab \oplus ac$                                                                                                                                                                       |

| Elément neutre                                                                                                                                        | Elément absorbant                                                                                                                   | Idempotence                                                                                                                                                                                                                                                                    |

| $a + 0 = a$ $1. a = a$ $a \oplus 0 = a$                                                                                                               | a+1=1 $0. a=0$                                                                                                                      | a + a = a $aa = a$                                                                                                                                                                                                                                                             |

| Complémentaire                                                                                                                                        | Lois de Morgan                                                                                                                      | Divers                                                                                                                                                                                                                                                                         |

| $a + \bar{a} = 1$ $a\bar{a} = 0$ $\bar{a}\bar{a} = \bar{a}$ $\bar{a} + \bar{a} = \bar{a}$ $\bar{a} = a$ $a \oplus \bar{a} = 1$ $a \oplus 1 = \bar{a}$ | $\frac{\overline{ab} = \overline{a} + \overline{b}}{\overline{a+b} = \overline{a}\overline{b}}$                                     | $a + ab = a(a + b) = a$ $a + (\bar{a}b) = a + b$ $a(\bar{a} + b) = ab$ $a \oplus a = 0$ $a \oplus \bar{b} = \bar{a} \oplus b = \bar{a} \oplus \bar{b}$ $\bar{a} \oplus \bar{b} = a \oplus b$ $a \oplus b = a\bar{b} + \bar{a}b$ $\bar{a} \oplus \bar{b} = ab + \bar{a}\bar{b}$ |

Table 1 : Tableau récapitulatif des règles de calcul logique [1]

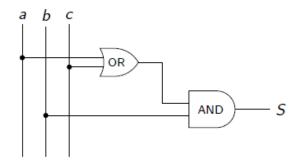

#### c. Construction et optimisation

#### i. Du circuit logique à la table de vérité :

Soit le schéma d'un circuit logique :

| а | b | С | a+c | S = b(a+c) |

|---|---|---|-----|------------|

| 0 | 0 | 0 | 0   | 0          |

| 0 | 0 | 1 | 1   | 0          |

| 0 | 1 | 0 | 0   | 0          |

| 0 | 1 | 1 | 1   | 1          |

| 1 | 0 | 0 | 1   | 0          |

| 1 | 0 | 1 | 1   | 0          |

| 1 | 1 | 0 | 1   | 1          |

| 1 | 1 | 1 | 1   | 1          |

⇒ La table de vérité correspondante.

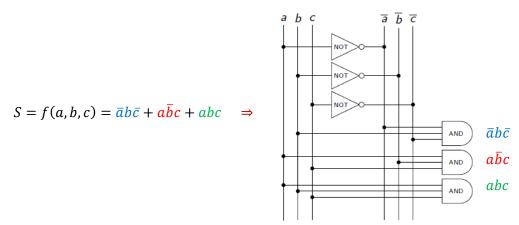

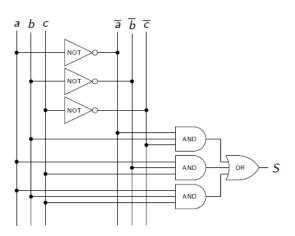

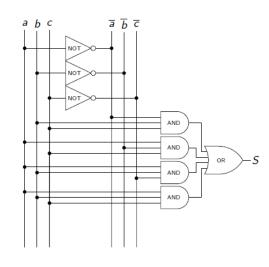

- ii. De la table de vérité au circuit logique :

- 1) Ecrire l'équation de la fonction à partir de sa table de vérité

| а | b | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

- Pour chaque cas où la sortie vaut 1 ajouter un « *minterme* » à la fonction.

- Un *minterme* est un AND de toutes les variables d'entrée de la fonction (éventuellement complémentées) :

- Si la variable d'entrée vaut 1, elle est écrite directement dans le *minterme*.

- o Si la variable d'entrée vaut 0, elle est complémentée dans le *minterme*.

$$\Rightarrow$$

$S = f(a, b, c) = \bar{a}b\bar{c} + a\bar{b}c + abc$

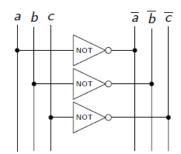

2) Réaliser la négation de toutes les variables d'entrée

- 3) Construire une porte AND pour chacun des *mintermes*.

- 4) Etablir le câblage des portes OR avec les entrées appropriées.

- 5) Réunir l'ensemble des sorties des portes AND vers une porte OR, dont la sortie et le résultat de la fonction.

- ➤ Remarque : ce circuit n'est pas optimal pour la table de vérité initiale. Il faut **simplifier** la fonction pour minimiser le nombre portes logiques.

#### iii.Simplification

- Diminuer le nombre d'opérateurs.

- Diminuer le nombre de portes logiques (et donc le coût).

Il y a deux approches de simplification :

- 1) Méthode algébrique (algèbre de Boole).

- Exemple : la fonction majoritaire ⇒ donne 1 en sortie si la majorité des bits en entrée sont des 1 sinon 0.

$$f(a,b,c) = \overline{a}bc + a\overline{b}c + abc + abc$$

$$= (\overline{a}b + a\overline{b})c + ab(c + \overline{c})$$

$$= (a + b)(\overline{a} + \overline{b})c + ab$$

$$= (ac + bc)\overline{ab} + ab$$

$$= (ab + ac + bc)(\overline{ab} + ab)$$

$$= ab + ac + bc$$

| а | b | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

- 2) Méthode des tableaux de Karnaugh

- O Permet de visualiser une fonction et d'en tirer naturellement une écriture simplifiée.

- Représentation de toutes les combinaisons d'états possibles pour un nombre de variables donné.

- Outil graphique qui permet de simplifier de manière méthodique des expressions booléennes.

- o Exploite le codage de l'information et la notion d'adjacence.

#### ✓ Principe:

- Mettre en évidence sur un graphique les *mintermes* ou *maxtermes* adjacents.

- Transformer les adjacences logiques en adjacences géométriques.

#### Table de vérité vs. Tableau de Karnaugh

1 ligne  $\Rightarrow$  1 case n variables  $\Rightarrow$  2<sup>n</sup> cases

- ✓ La méthode passe par trois phases :

- 1) Transcription de la fonction dans un tableau codé.

- 2) Recherche des adjacences pour simplification.

- 3) Mise en équations des groupements effectués.

- **Exemple**: fonction majoritaire

- 1) Ecrire la table de vérité sous la forme d'un code de Gray (ou binaire réfléchi) : les valeurs des entrées ne diffèrent que d'un seul bit entre chaque ligne.

| а | b | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

$\Rightarrow$

| а | b | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 |

Table Initiale

Code de Gray

2) Compacter la table : représenter la sortie en fonctions des entrées sous forme d'un tableau à 2 dimensions.

| а | b | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 |

$\Rightarrow$

| bc<br>a | 00 | 01 | 11 | 10 |

|---------|----|----|----|----|

| 0       | 0  | 0  | 1  | 0  |

| 1       | 0  | 1  | 1  | 1  |

- 3) Regrouper tous les bits 1 de telle sorte que :

- Les bits 1 d'un groupe sont adjacents ou des bords du tableau.

- La taille des groupes est une puissance de 2.

- Un groupe contient le plus de 1 possible.

| bc<br>a | 00 | 01 | 11  | 10 |

|---------|----|----|-----|----|

| 0       | 0  | 0  | 1   | 0  |

| 1       | 0  | 1  | (1) | 1  |

- 4) En déduire la formule et le circuit :

- La formule est la somme (OR) des *mintermes*.

- Un minterme est le produit (AND) des variables du même groupe de bits :

- O Des variables qui valent toujours 1 dans ce groupe.

- O Des négations de celles qui valent toujours 0.

- o Les autres variables n'apparaissent pas dans le produit.

| bc<br>a | 00 | 01 | 11  | 10 |

|---------|----|----|-----|----|

| 0       | 0  | 0  | 1   | 0  |

| 1       | 0  | 1  | (1) | 1) |

$$\Rightarrow$$

$S = f(a, b, c) = bc + ac + ab$

#### 2. Circuits combinatoires

# a. Définitions

Les circuits combinatoires sont des circuits logiques combinés pour obtenir un nouveau circuit avec une fonction logique plus complexe. Ils sont nés du besoin de circuits logiques à plusieurs entrées et plusieurs sorties, et parfois des sorties qui dépendent d'entrées supplémentaires dites de sélection.

# b. Caractéristiques

Un circuit combinatoire est caractérisé par :

- Les entrées :

- O Les données : ne sont pas des entrées de la table de vérité.

- o Les paramètres : bits de réglage.

- o Les variables d'entrée.

- La sortie : pas forcément unique !

- o Fonction logique : une seule valeur en sortie.

- o Circuit: plusieurs fonctions possibles pour obtenir le comportement voulu.

- Le rôle de différents éléments :

- o A quoi sert le circuit ?

- O Qu'obtient-on en sortie?

- O Quel rôle jouent les entrées ?

- La table de vérité (une table par fonction).

- ► Exemple : la fonction majoritaire

| а | b | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 |

- ► Problème : sur un nombre pair d'entrées, une seule sortie ne suffit pas :

- o Soit les 0 sont majoritaires (sortie 00)

- o Soit les 1 sont majoritaires (sortie 01)

- O Soit il n'y a pas de majoritaire (sortie 10)

- ▶ Solution : circuit combinatoire à 4 entrées et 2 sorties S<sub>0</sub> et S<sub>1</sub>.

| а | b | С | d | $S_0$ | $S_1$ |

|---|---|---|---|-------|-------|

| 0 | 0 | 0 | 0 | 0     | 0     |

| 0 | 0 | 0 | 1 | 0     | 0     |

| 0 | 0 | 1 | 0 | 0     | 0     |

| 0 | 0 | 1 | 1 | 1     | 0     |

| 0 | 1 | 0 | 0 | 0     | 0     |

| 0 | 1 | 0 | 1 | 1     | 0     |

| 0 | 1 | 1 | 0 | 1     | 0     |

| 0 | 1 | 1 | 1 | 0     | 1     |

| 1 | 0 | 0 | 0 | 0     | 0     |

| 1 | 0 | 0 | 1 | 1     | 0     |

| 1 | 0 | 1 | 0 | 1     | 0     |

| 1 | 0 | 1 | 1 | 0     | 1     |

| 1 | 1 | 0 | 0 | 1     | 0     |

| 1 | 1 | 0 | 1 | 0     | 1     |

| 1 | 1 | 1 | 0 | 0     | 1     |

| 1 | 1 | 1 | 1 | 0     | 1     |

# c. Circuits combinatoires de base

Les circuits combinatoires les plus communs :

- Le multiplexeur

- Le démultiplexeur

- Le décodeur

- Le comparateur

•

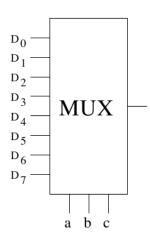

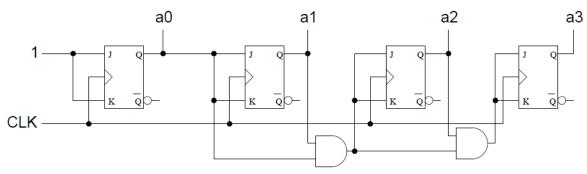

i. Le multiplexeur  $2^n \times n$

- Entrées :

- o  $2^n$  lignes d'entrée (données) :  $D_0$ , ...,  $D_{2^{n}-1}$

- o n lignes de sélection : a, b, c, ...

- **Sortie** : une seule sortie *S*.

- Rôle : aiguiller la valeur de l'une des 2<sup>n</sup> lignes d'entrée vers la sortie

S.

La ligne d'entrée choisie est désignée grâce aux bits de sélection.

| а | b | С | S     |

|---|---|---|-------|

| 0 | 0 | 0 | $D_0$ |

| 0 | 0 | 1 | $D_1$ |

| 0 | 1 | 0 | $D_2$ |

| 0 | 1 | 1 | $D_3$ |

| 1 | 0 | 0 | $D_4$ |

| 1 | 0 | 1 | $D_5$ |

| 1 | 1 | 0 | $D_6$ |

| 1 | 1 | 1 | $D_7$ |

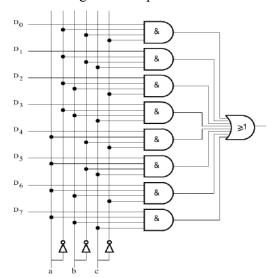

► Câblage du multiplexeur 8 × 3

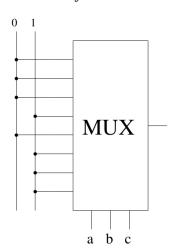

Exemple d'utilisation du multiplexeur : La fonction majoritaire avec un multiplexeur

| а | b | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 |

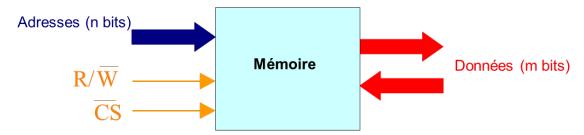

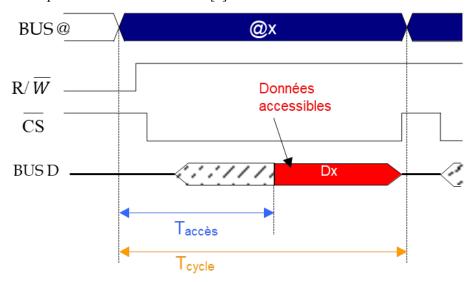

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 |

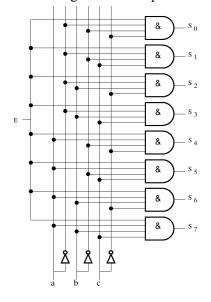

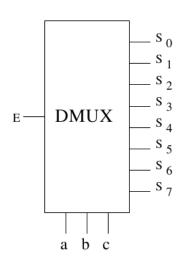

ii. Le démultiplexeur  $2^n \times n$

# • Entrées :

$\circ$  une lignes d'entrée (donnée) : E

o n lignes de sélection : a, b, c, ...

• **Sortie**:  $2^n$  lignes de sortie  $S_0, ..., S_{2^n-1}$

• **Rôle** : aiguiller l'entrée E vers l'une des  $2^n$  lignes de sortie.

La ligne de sortie est désignée grâce aux bits de sélection.

| а | b | С | $S_0$ | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | <i>S</i> <sub>7</sub> |

|---|---|---|-------|-------|-------|-------|-------|-------|-------|-----------------------|

| 0 | 0 | 0 | Ε     | 0     | 0     | 0     | 0     | 0     | 0     | 0                     |

| 0 | 0 | 1 | 0     | Е     | 0     | 0     | 0     | 0     | 0     | 0                     |

| 0 | 1 | 0 | 0     | 0     | Е     | 0     | 0     | 0     | 0     | 0                     |

| 0 | 1 | 1 | 0     | 0     | 0     | Ε     | 0     | 0     | 0     | 0                     |

| 1 | 0 | 0 | 0     | 0     | 0     | 0     | Е     | 0     | 0     | 0                     |

| 1 | 0 | 1 | 0     | 0     | 0     | 0     | 0     | Ε     | 0     | 0                     |

| 1 | 1 | 0 | 0     | 0     | 0     | 0     | 0     | 0     | Е     | 0                     |

| 1 | 1 | 1 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | Е                     |

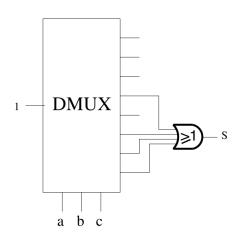

► Câblage du démultiplexeur 8 × 3

Exemple d'utilisation du démultiplexeur : La fonction majoritaire avec un démultiplexeur

| а | b | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 |

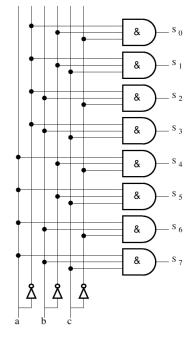

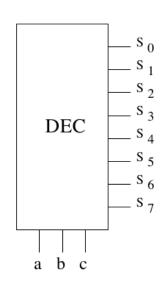

iii. Le décodeur  $2^n \times n$

• Entrées : *n* lignes de sélection : *a*, *b*, *c*, ...

• **Sortie**:  $2^n$  lignes de sortie  $S_0, ..., S_{2^n-1}$

• **Rôle** : sélectionner (mettre à 1) l'une des 2<sup>n</sup> lignes de sortie. La ligne de sortie est désignée grâce aux bits de sélection.

| а | b | С | $S_0$ | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | <i>S</i> <sub>7</sub> |

|---|---|---|-------|-------|-------|-------|-------|-------|-------|-----------------------|

| 0 | 0 | 0 | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0                     |

| 0 | 0 | 1 | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0                     |

| 0 | 1 | 0 | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0                     |

| 0 | 1 | 1 | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0                     |

| 1 | 0 | 0 | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0                     |

| 1 | 0 | 1 | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0                     |

| 1 | 1 | 0 | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0                     |

| 1 | 1 | 1 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                     |

► Câblage du décodeur 8 × 3

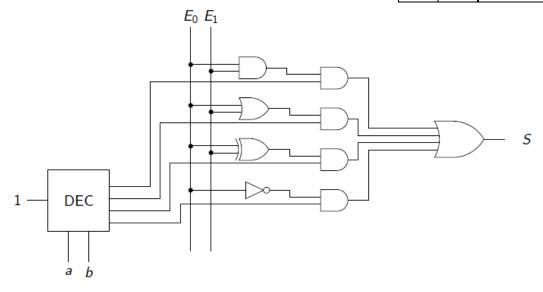

▶ Exemple d'utilisation d'un décodeur : activation de fonction

Ce circuit fait, au choix, l'une des 4 fonctions logiques (AND, OR, XOR, NOT) sur les données  $E_0$  et  $E_1$ . Le choix de la fonction est déterminé par les valeurs de a et b selon la table de vérité suivante :

| а | D | 3                |

|---|---|------------------|

| 0 | 0 | $E_0 \times E_1$ |

| 0 | 1 | $E_0 + E_1$      |

| 1 | 0 | $E_0 \oplus E_1$ |

| 1 | 1 | $\overline{E_0}$ |

Réaliser le circuit logique correspondant en utilisant un décodeur

# 3. Circuits arithmétiques

Les circuits arithmétiques sont des circuits combinatoires permettant d'effectuer des opérations arithmétiques sur les nombres en entrée. Les circuits arithmétiques de base sont :

- L'additionneur / Le soustracteur

- L'incrémenteur / Le décrémenteur

- Le décaleur

- L'Unité Arithmétique et Logique (UAL)

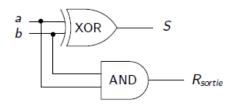

#### a. Demi-additionneur

- **Entrées** : les 2 bits à additionner a et b.

- Sorties :

- $\circ$  La somme S = a + b.

- La retenue de sortie  $R_{sortie}$ .

- **Rôle** : Additionner *a* et *b* en conservant la retenue.

| а | b | S | $R_{sortie}$ |

|---|---|---|--------------|

| 0 | 0 | 0 | 0            |

| 0 | 1 | 1 | 0            |

| 1 | 0 | 1 | 0            |

| 1 | 1 | 0 | 1            |

▶ Problème : si plusieurs additions successives, comment reporter la retenue ?

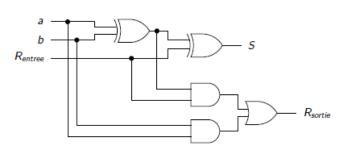

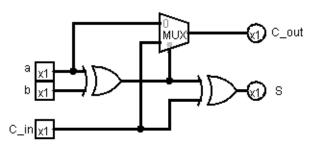

# b. Additionneur complet

- Entrées :

- O Les 2 bits à additionner a et b.

- O La retenue d'entrée Rentrée

- Sorties :

- o La somme  $S = a + b + R_{entrée}$

- $\circ$  La retenue de sortie  $R_{sortie}$

- **Rôle** : Additionner a et b en prenant en compte la retenue d'entrée  $R_{entrée}$  et en conservant la retenue de sortie  $R_{sortie}$

| а | b | $R_{entr\'ee}$ | S | $R_{sortie}$ |

|---|---|----------------|---|--------------|

| 0 | 0 | 0              | 0 | 0            |

| 0 | 0 | 1              | 1 | 0            |

| 0 | 1 | 0              | 1 | 0            |

| 0 | 1 | 1              | 0 | 1            |

| 1 | 0 | 0              | 1 | 0            |

| 1 | 0 | 1              | 0 | 1            |

| 1 | 1 | 0              | 0 | 1            |

| 1 | 1 | 1              | 1 | 1            |

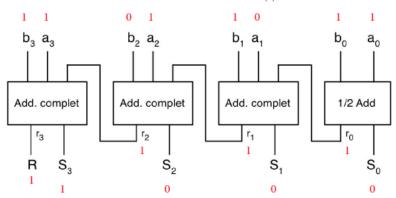

# ► Exemple : Additionneur 4 bits

Soit 2 nombres à additionner :  $A = a_3 a_2 a_1 a_0 = 1 1 0 1_{(2)}$   $B = b_3 b_2 b_1 b_0 = 1 0 1 1_{(2)}$

Arr S = A + B = S<sub>3</sub> S<sub>2</sub> S<sub>1</sub> S<sub>0</sub> = 1 0 0 0<sub>(2)</sub> avec retenue R = 1.

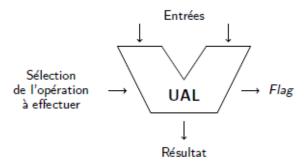

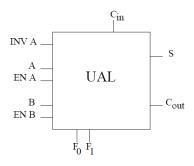

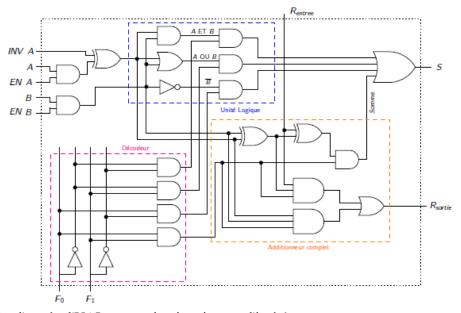

# c. Unité Arithmétique et Logique

L'unité arithmétique et logique est l'organe responsable des calculs arithmétiques effectué par le processeur.

Elle est composée d'un ensemble de circuits combinatoires.

#### • Entrées :

- o A et B : les variables (données)

- $\circ$  F<sub>0</sub> et F<sub>1</sub>: bits de choix du signal d'activation

- o R<sub>entrée</sub> (C<sub>in</sub>) : la retenue d'entrée

- EN A et EN B : les bits inhibiteurs de A et B (optionnel)

- o INV A: pour obtenir A (optionnel)

#### • Sorties:

- O S: le résultat de l'opération

- $\circ$  R<sub>sortie</sub> (C<sub>out</sub>): la retenue de sortie

- Rôle: Faire l'une des 4 opérations (en fonction des bits d'activation choisis):

- o A ET B

- o AOUB

- o NON B

- A+B+R<sub>entrée</sub>

Pour 2 bits d'entrée, l'UAL est un circuit qui a peu d'intérêt . . .

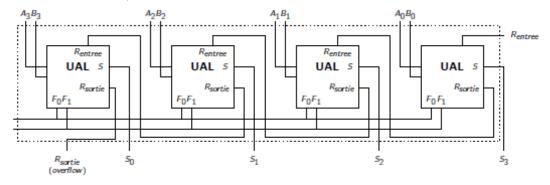

# ▶ UAL à *n* bits :

- En connectant les retenues de *n* UALs, on obtient une UAL *n* bits telle que :

- O Les opérations logiques sont des opérations bit à bit.

- Les opérations arithmétiques sont effectuées sur des entiers en complément à 2 sur n bits.

# ► Exemple UAL à 4 bits :

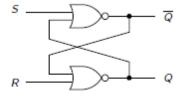

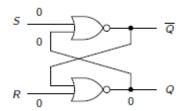

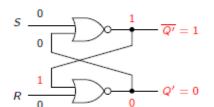

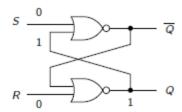

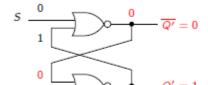

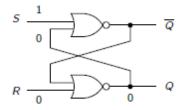

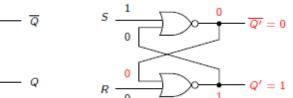

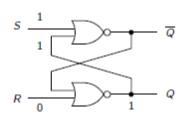

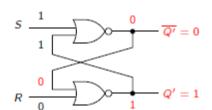

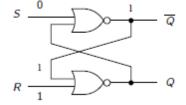

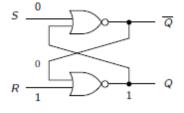

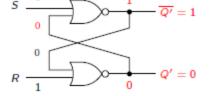

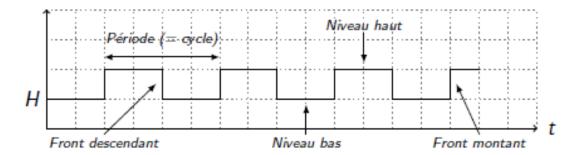

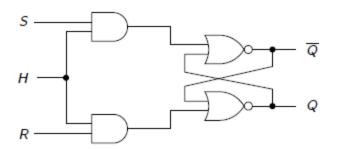

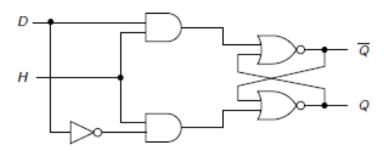

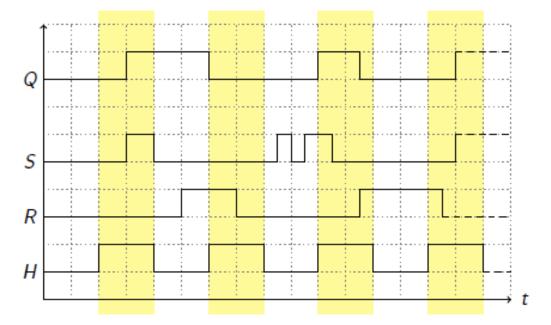

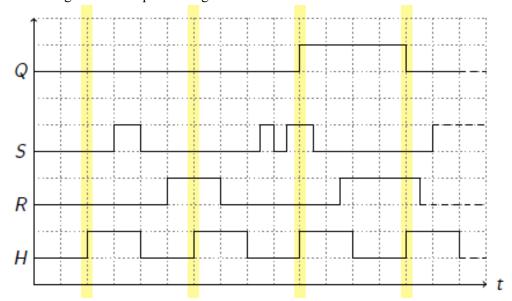

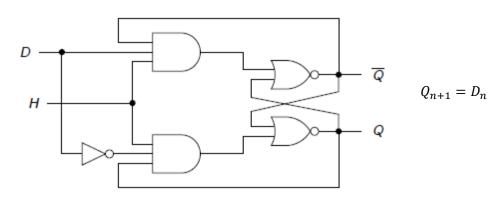

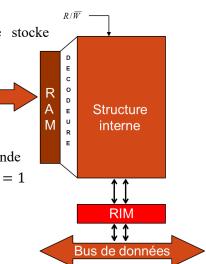

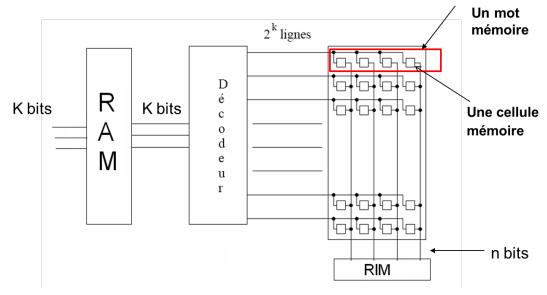

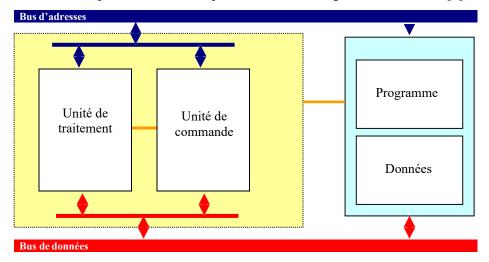

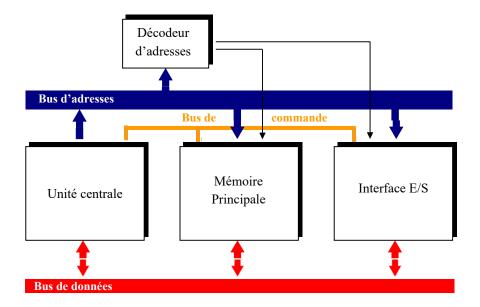

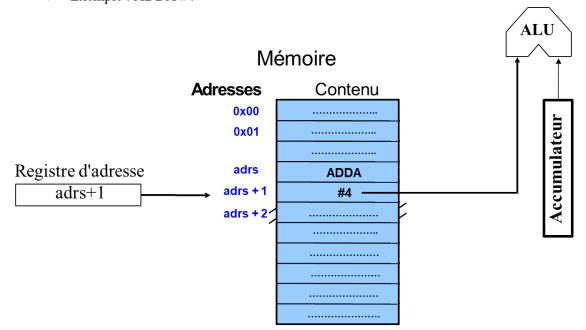

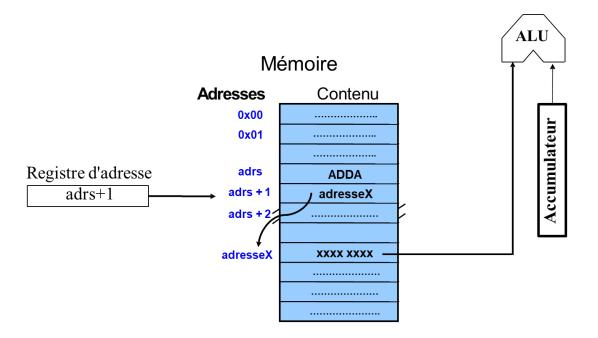

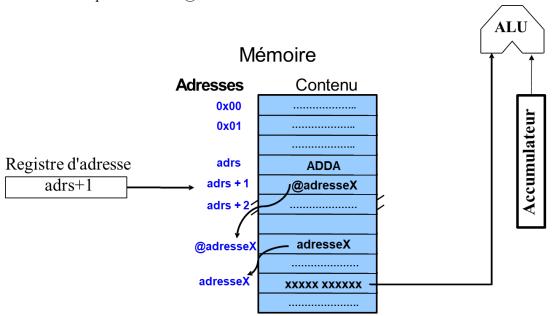

On souhaite faire l'addition entre A et B (données) telle que :